자동 등록 확인

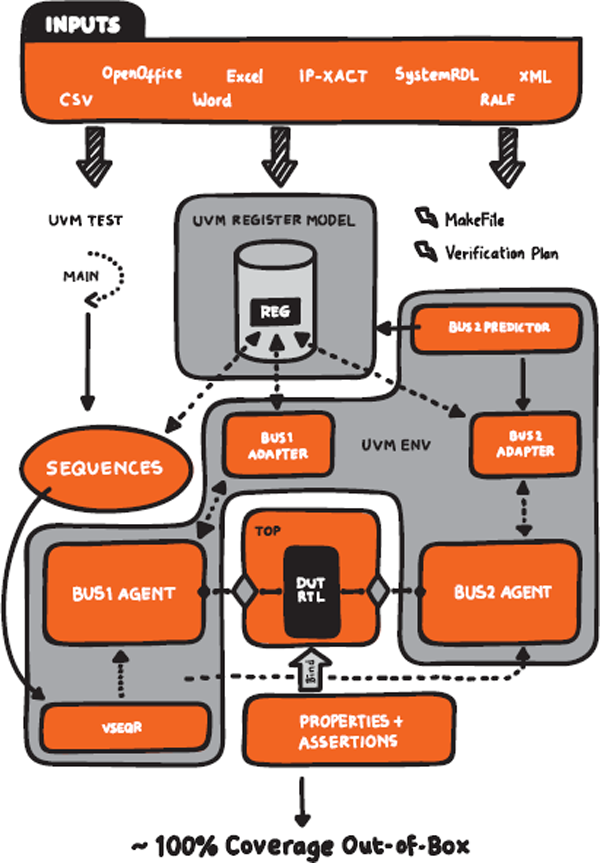

우리의 솔루션은 레지스터에 대해 100 % 기능 커버리지를 제공하는 UVM 기반 검증 환경을 만드는 지루한 노력을 자동화 시켜줍니다. 제약 조건 임의 자극 생성, 다양한 레지스터 동작 시나리오에 대한 불법적인 bin의 자동 생성을 사용하여 보다 신속한 범위 폐쇄를 얻을 수 있습니다.

황금 사양을 기반으로 시뮬레이션을 통해 검증을 위해 다음을 생성할 수 있습니다.

구성 요소, hdl_paths, 커버 그룹, 제약 조건 및 불법적인 저장소를 포함한 완전하고 완벽한 UVM 테스트 환경

양성 및 음성 기능성을 위한 서열

"Makefile"(VCS, Incisive 또는 Questa의 경우) 시뮬레이션을 실행하고 사용 중인 시뮬레이터에 적합한 시뮬레이션 데이터베이스의 결과를 수집합니다.

시뮬레이션 및 커버리지 결과에 주석을 달 수 있는 검증 계획(Verification Plan)

황금 사양을 기반으로 시뮬레이션을 통해 검증을 위해 다음을 생성할 수 있습니다.

구성 요소, hdl_paths, 커버 그룹, 제약 조건 및 불법적인 저장소를 포함한 완전하고 완벽한 UVM 테스트 환경

양성 및 음성 기능성을 위한 서열

"Makefile"(VCS, Incisive 또는 Questa의 경우) 시뮬레이션을 실행하고 사용 중인 시뮬레이터에 적합한 시뮬레이션 데이터베이스의 결과를 수집합니다.

시뮬레이션 및 커버리지 결과에 주석을 달 수 있는 검증 계획(Verification Plan)

주요 혜택

레지스터 중심의 커버리지 리포트를 통해 100% 기능 커버리지를 제공합니다.

검증 주기를 크게 줄입니다.

잠금, 그림자, 별칭 및 인터럽트 레지스터를 비롯한 특수 레지스터의 시퀀스를 생성합니다.

IP-XACT, SystemRDL, RALF, Word, Excel, CSV 또는 XML / YAML을 가져올 수 있는 IDesignSpec™의 추가 기능

검증 주기를 크게 줄입니다.

잠금, 그림자, 별칭 및 인터럽트 레지스터를 비롯한 특수 레지스터의 시퀀스를 생성합니다.

IP-XACT, SystemRDL, RALF, Word, Excel, CSV 또는 XML / YAML을 가져올 수 있는 IDesignSpec™의 추가 기능

황금 사양을 기반으로 정식 검증을 위해 다음 코드를 생성할 수도 있습니다.

SystemVerilog 속성 및 어서션을 사용하여 레지스터 액세스 정책 및 버스 프로토콜 준수 확인

어설션(assertion)을 사용하여 DUT RTL 및 써드 파티 설계 IP를 바인딩하는 최상위 파일

Makefile 또는 TCL 명령 스크립트

엔지니어가 결과를 분석할 수 있도록 이러한 공식적인 결과에 백-주석(back annotate)을 달 수 있는 검증 계획

펌웨어 / 검증을 위한 포괄적인 C/C++ 테스트

SystemVerilog 속성 및 어서션을 사용하여 레지스터 액세스 정책 및 버스 프로토콜 준수 확인

어설션(assertion)을 사용하여 DUT RTL 및 써드 파티 설계 IP를 바인딩하는 최상위 파일

Makefile 또는 TCL 명령 스크립트

엔지니어가 결과를 분석할 수 있도록 이러한 공식적인 결과에 백-주석(back annotate)을 달 수 있는 검증 계획

펌웨어 / 검증을 위한 포괄적인 C/C++ 테스트